摘要

隨著物聯網互連裝置和 5G 連接等技術創新成為我們日常生活的一部分,監管這些裝置的電磁輻射並量化其 EMI 抗擾度的需求也隨之增加。滿足 EMC 合規目標通常是一項複雜的工作。本文介紹如何透過開源 LTspice® 模擬電路來回答以下關鍵問題:(a) 我的系統能否通過 EMC 測試,或者是否需要增加緩解技術?(b) 我的設計對外部環境雜訊的抗擾度如何?

為何要使用 LTspice 進行 EMC 模擬?

針對 EMC 的設計應該盡可能遵循產品發布時程表,但事實往往並非如此,因為 EMC 問題和實驗室測試可能將產品發布延遲數月。

通常,模擬側重於電子設備的功能方面;但是,諸如 LTspice 之類簡單的開源工具也可以用來模擬任何裝置的 EMC 行為。由於許多人在家工作,並且 EMC 實驗室的成本高昂(每天高達 2000 美元),因此準確的 EMC 模擬工具更顯價值。花幾個小時對 EMC 故障和電路修復情況進行模擬,有助於避免多次實驗室測試迭代和昂貴的硬體重新設計。

為了發揮作用,EMC 模擬工具需要盡可能準確。本系列文章會提供一些指南和 LTspice EMC 電路模型,這些模型經過模擬並與實際實驗室測量結果非常吻合。

這是三篇系列文章的第一部分,這些文章為一個範例感測器訊號鏈提供了 EMC 模擬模型,其核心是 MEMS 振動感測器。不過,許多元件和 EMC 模擬技術並非 MEMS 解決方案所獨有的,而是可以廣泛用於各種應用。

-

第 1 部分:電源元件與傳導輻射和抗擾度。

-

第 2 部分:電纜驅動收發器鏈路上的訊號完整性和瞬變穩健性。

-

第 3 部分:訊號調節元件及如何提高對外部雜訊的抗擾度。

使用 LTspice 解決輻射和抗擾度問題

閱讀本文後,您應該能夠回答以下關鍵問題:

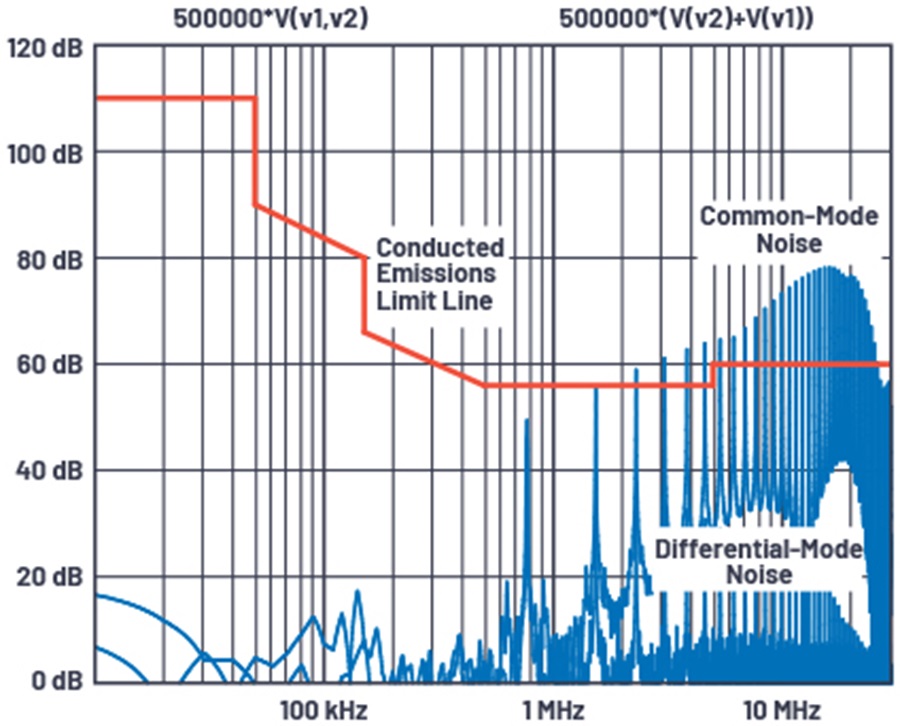

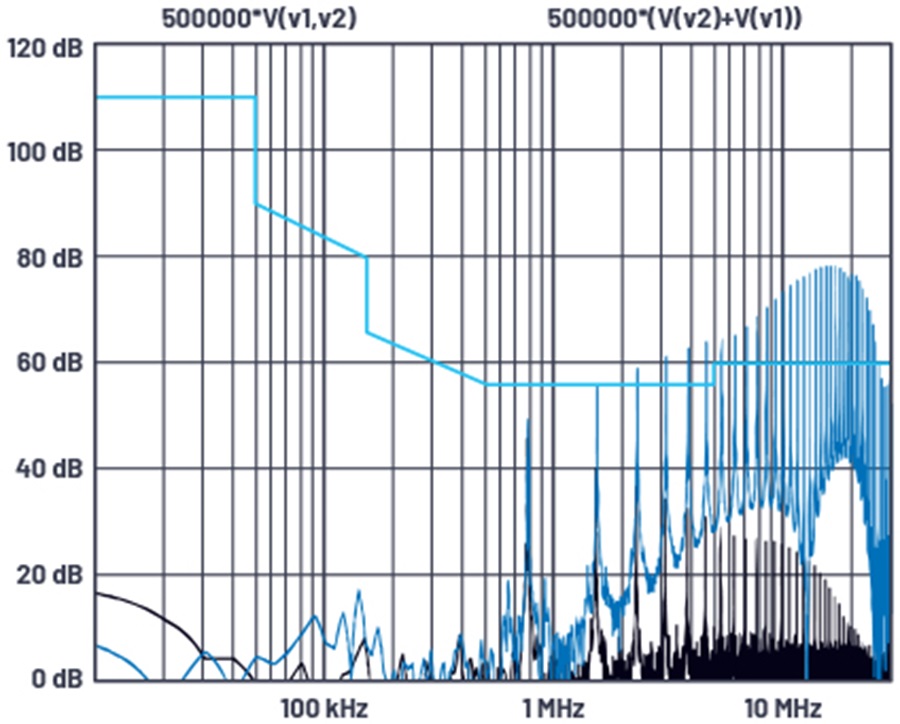

(a) 我的系統是否有可能通過 EMC 測試?是否應該為共模電感、濾波電感或電容預留空間? 閱讀本文後,您應該能夠使用 LTspice 繪製降壓轉換器電源設計的差模和共模雜訊圖,並展示電路超過(失敗)還是未超過(成功)傳導輻射標準限值,如圖 1 所示。

圖 1. 差模和共模雜訊的 LTspice圖,附有傳導輻射限值線

(b) 是否需要線性穩壓器來為敏感負載提供穩定的電壓? 閱讀本文後,基於設計容許的降壓輸出漣波電壓準位,您應該能夠使用 LTspice 了解降壓轉換器的輸出端是否需要 LDO 穩壓器。此外,本文還提供了一個可配置的電源抗擾度 (PSRR) 測試電路。

用於感測器的降壓轉換器

MEMS 振動感測器通常被置於一個小型金屬外殼中,其直徑通常為 20 mm 至 30 mm,高度為 50 mm 至 60 mm。帶有數位訊號鏈的感測器通常由長電纜提供 9 VDC 至 30 VDC 電源,功耗低於 300 mW。為了能放入這種小型外殼內,需要高效率、寬輸入範圍的微型電源解決方案。

LT8618、LT8618-3.3 和 LT8604 是緊湊型高速降壓開關穩壓器,非常適合 MEMS 感測器應用。LT8618 和 LT8618-3.3 已有相應的 LTspice 模型。LT8618 具有良好的穩壓能力,提供非常低的輸出漣波,其峰對峰值小於 10 mV。然而,輸出電容組的寄生電阻和電感會增加這種漣波,導致降壓電路產生有害的傳導輻射。電容性負載、降壓穩壓器的輸出開關寄生效應以及 PCB 設計和感測器外殼之間的耦合電容,都可能引起寄生效應。

提取和使用寄生值

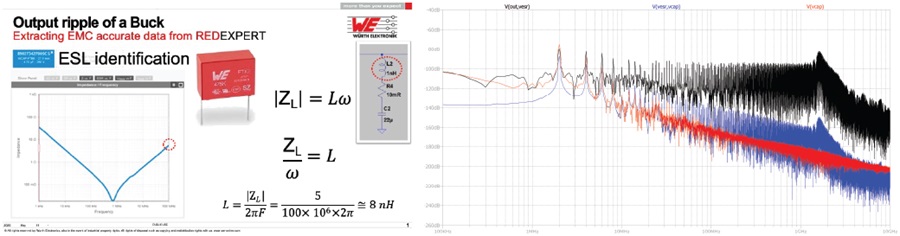

接下來介紹工程師如何使用 Würth REDEXPERT 從實際電容中提取 ESL 和 ESR 寄生值,並使用 LTspice 進行電路模擬。在許多系統的輸入端和輸出端,電容和電感的寄生效應對 EMI 性能起著重要作用。為了降低系統輸出漣波,分離各種寄生貢獻有助於使用者做出最佳選擇。

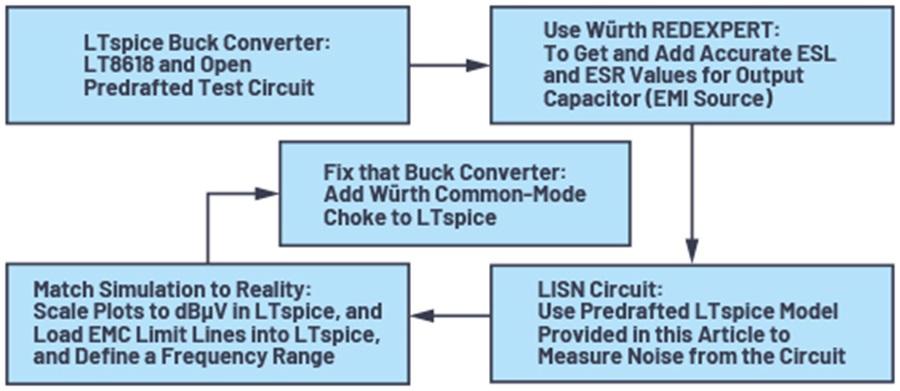

我們使用 LTspice 和 Würth REDEXPERT 流程來討論降壓轉換器的傳導輻射模擬,如圖 2 所示。對於降壓轉換器,通常來說,輸出漣波與訊噪比 (SNR) 相關,而輸入漣波與 EMC 性能密切相關。

圖 2. 使用 LTspice 進行傳導輻射模擬的流程

概述圖 2 所示的模擬方法之後,本文將使用 DC2822A LT8618 展示板進行實際的實驗室測量和模擬相關性分析。

使用 Würth REDEXPERT 數據的 LTspice 測試電路

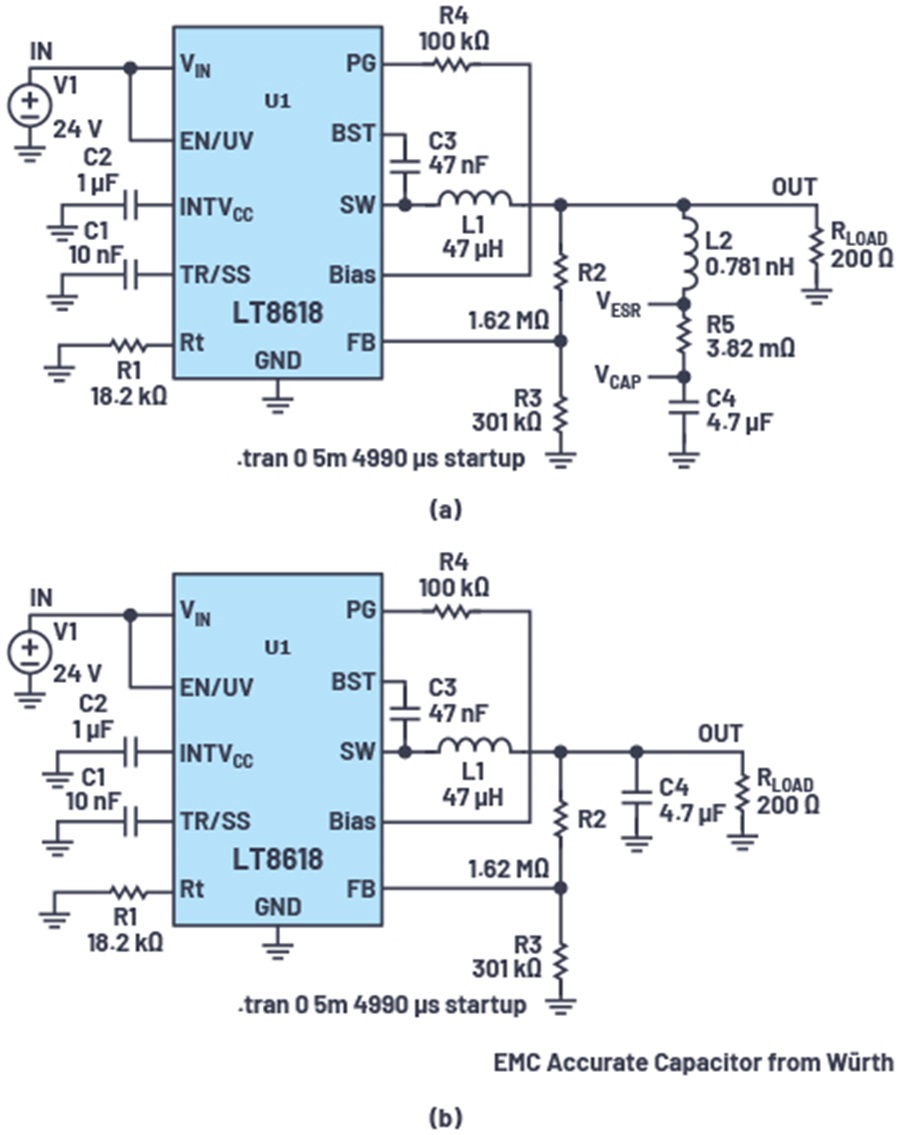

降壓轉換器的輸出漣波電壓是電容阻抗和電感電流的函數。為了獲得更好的模擬精度,可以使用 Würth REDEXPERT 來選擇 4.7 µF 輸出電容 (885012208040),並提取隨頻率變化的 ESR 和 ESL。ESL 和 ESR 有時會被載入到 LTspice 電容模型中,但快速檢查將證明 LTspice 電容數據經常會忽略 ESL。圖 3a 和 3b 顯示了兩個等效電路:(a) 使用 4.7 µF 輸出電容以及分離的 ESL 和 ESR 值;(b) 使用包含 ESR 和 ESL 參數的 Würth 電容。

圖 3. LTspice 測試電路:(a) 使用 4.7 μF 電容以及分離的 ESL 和 ESR 值;(b) 使用包含 ESR 和 ESL 參數的 Würth 電容

REDEXPERT 顯示了許多元件的隨頻率而變化的阻抗,以幫助確定每個被動元件的關鍵寄生效應。這些寄生值稍後可以在 LTspice 模型中實現,從而能夠單獨評估其對總電壓漣波的貢獻。

如前所述,LT8618 提供非常低的輸出漣波,峰對峰值小於 10 mV。但是,當模擬電容性負載和 ESL 的影響時,輸出漣波電壓為 44 mV p-p。在頻率範圍內,電容 ESL 對雜訊的貢獻相當大,如圖 4 的 FFT 圖所示。

圖 4. FFT 圖顯示了一個 4.7 μF 電容的純電容、ESL 和 ESR 各自對頻譜的貢獻

使用 LTspice LISN 電路評估降壓輸入端的 EMI 合規性

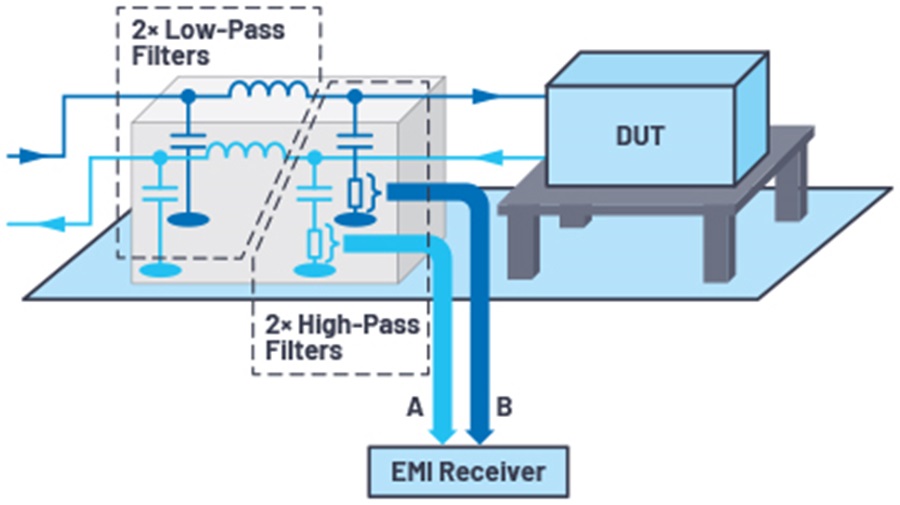

為了評估傳導設置中的 EMC 合規性,大多數標準依賴於電源阻抗穩定網路 (LISN) 或人工電源網路 (AMN)。這些裝置具有類似的功能,位於電路電源和待測物 (DUT)——這裡是降壓轉換器——之間。LISN/AMN 由低通和高通濾波器組成。低通濾波器提供從低頻電源(直流至幾百赫茲)到 DUT 的路徑。高通濾波器用於測量電源和返回電源線雜訊。這些電壓是在 50 Ω 電阻上測量,如圖 5 和圖 6 所示。在實際實驗室中,該電壓使用 EMI 接收器來測量。LTspice 可用來探測雜訊電壓並繪製傳導輻射測試頻譜圖。

圖 5. LISN 置於電源和待測物 (DUT) 之間

圖 6. LISN 內部的共模和差模干擾的表示

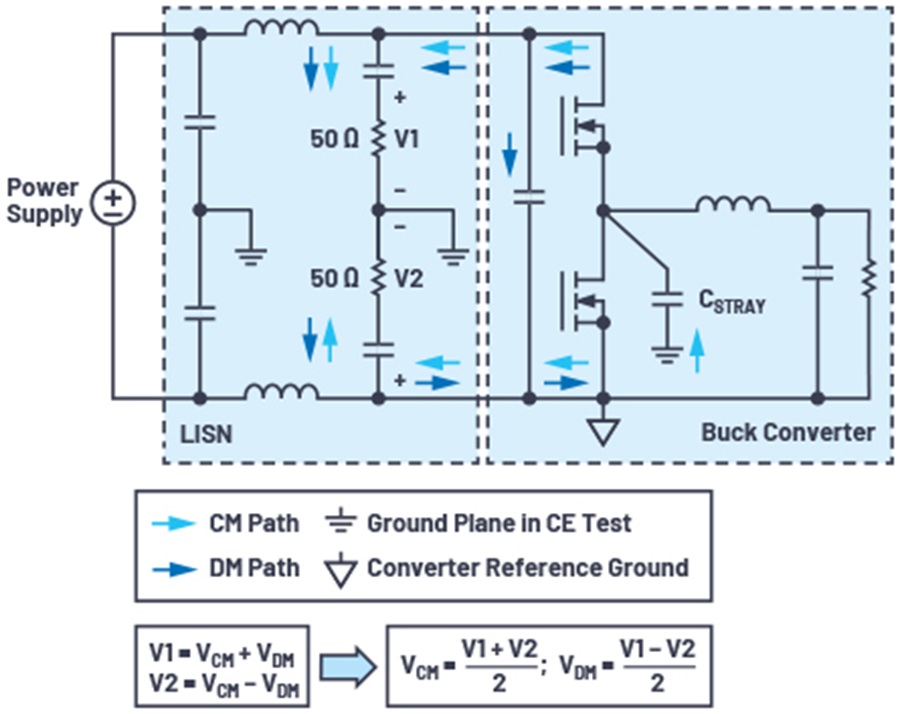

傳導輻射可分為兩類:共模 (CM) 雜訊和差模 (DM) 雜訊。區分 CM 和 DM 雜訊很重要,因為 EMI 緩解技術可能對 CM 雜訊有效,但對 DM 雜訊無效,反之亦然。由於 V1 和 V2 電壓同時輸出,因此在傳導輻射測試中可以使用 LISN 來分離 CM 和 DM 雜訊,如圖 6 所示。

DM 雜訊在電源線和返回線之間產生,而 CM 雜訊是透過雜散電容 $C_{STRAY}$ 在電源線和接地參考平面(例如銅測試台)之間產生。$C_{STRAY}$ 實際上模擬了降壓轉換器輸出端的開關雜訊寄生效應。

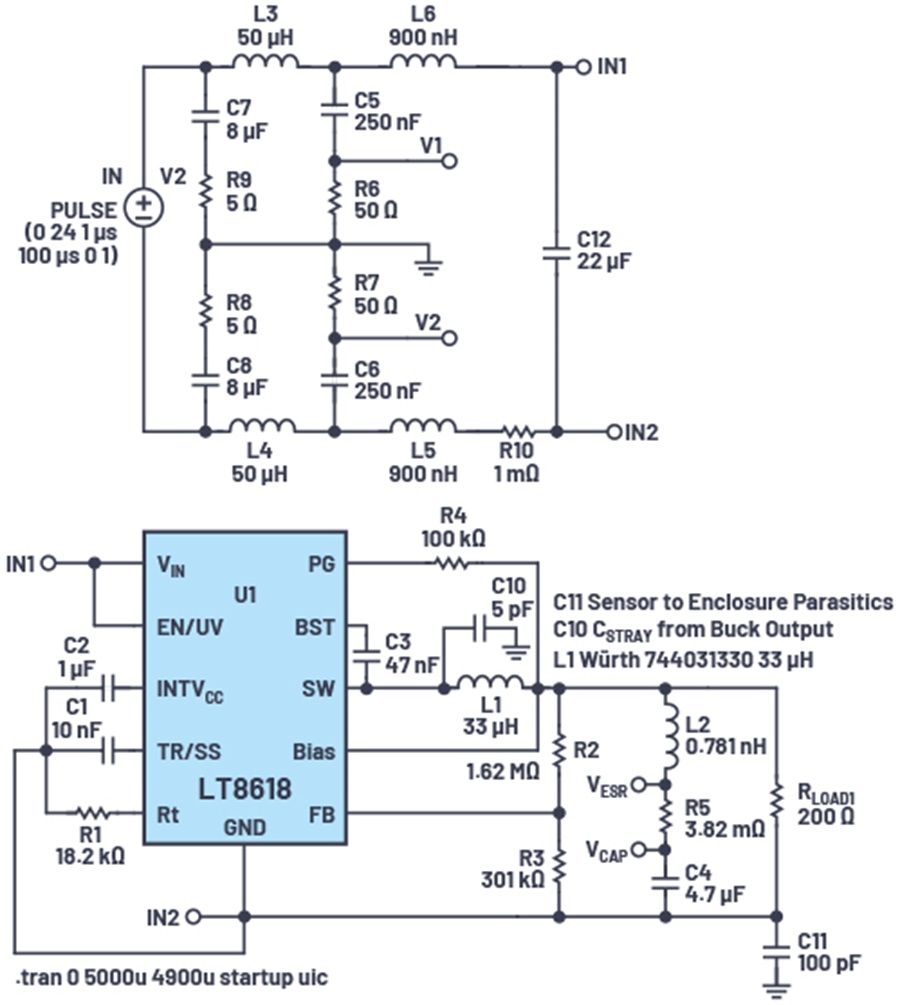

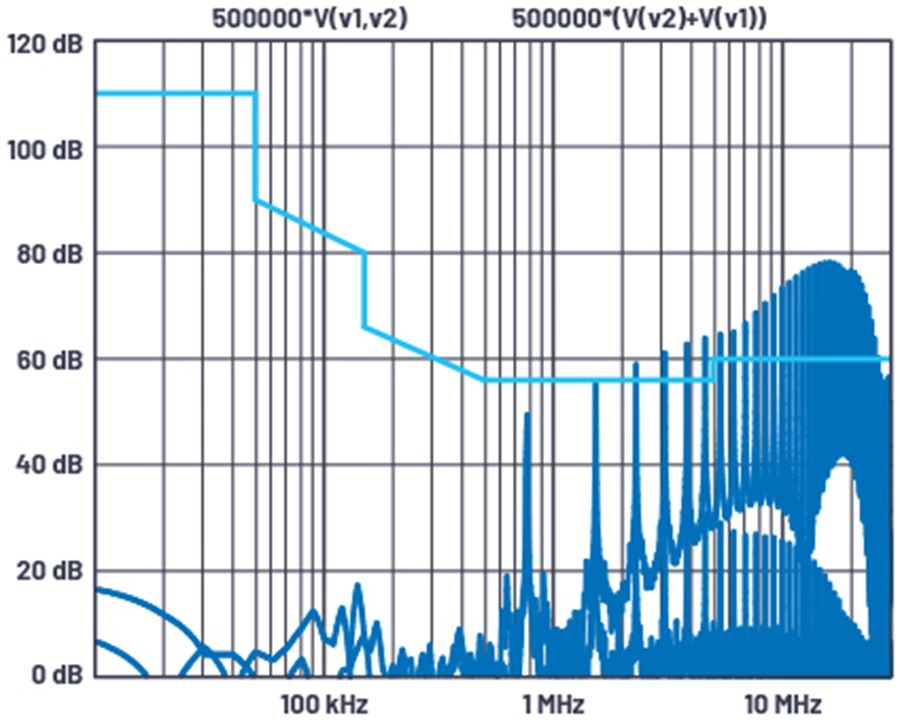

圖 6 對應的 LTspice LISN 電路如圖 7 所示。為了獲得更高的模擬精度,使用 L5 和 L6 電感來模擬 LISN 電源引線到測試電路的電感。電阻 R10 模擬測試板開槽接地層的阻抗。圖 7 還包括用於模擬 $C_{STRAY}$ 的電容 C10。電容 C11 模擬感測器 PCB 和感測器機械外殼之間的寄生電容。

圖 7. LTspice LISN 電路、LT8618 降壓轉換器和寄生建模

執行模擬時,應設定 LTspice 以幫助 LISN 電路更快達到穩定狀態,因為啟動條件選擇錯誤可能導致長期持續振盪。

確保取消勾選 "Start External DC Supply Voltages at Zero"(從零啟動外部直流電源電壓),並根據需要指定電路元件的初始條件(電壓和電流)。

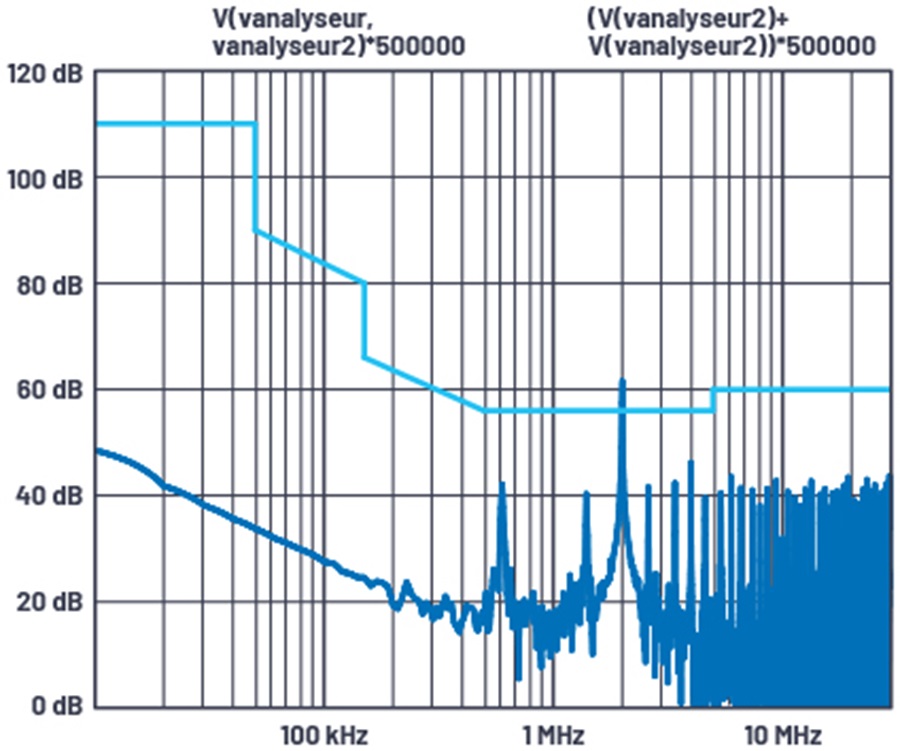

圖 8 顯示了 CM 和 DM 雜訊,使用的是從 LISN 端子 V1 和 V2 測得的 LTspice FTT 圖。為了再現圖 6 所示的算術運算,對於 DM 雜訊,V1 和 V2 相減後乘以 0.5;對於 CM 雜訊,V1 與 V2 相加,結果乘以 0.5。

圖 8. DM 雜訊(黑色)和 CM 雜訊(藍色)的 LTspice FFT 圖

在實驗室中,傳導輻射通常以 $dB\mu V$ 為單位進行測量,而 LTspice 的預設單位為 $1\ dBV$。兩者之間的關係為 $1\ dBV = 120\ dB\mu V$。

因此,DM 雜訊(以 $dB\mu V$ 為單位)的 LTspice 表達式為:

CM 雜訊的表達式為:

添加傳導輻射限值線

LTspice FFT 波形檢視參數可以透過繪圖設定檔進行編輯。使用 LTspice FFT 選單,導航到 "Save Plot Settings"(儲存繪圖設定)並點擊儲存。繪圖設定檔可以使用文字編輯器開啟,並且可以進行操作以添加 EN 55022 傳導輻射限值線以及相關的 EMC 頻率範圍(10 kHz 至 30 MHz)和振幅(0 dBµV 至 120 dBµV)。

EN 55022 傳導輻射標準頻率和振幅限值可以利用 Excel 進行操作,以提供正確的語法來複製和貼上到 LTspice 繪圖設定檔,如圖 9 所示。線定義可以貼上到繪圖設定參數中,如圖 10 所示。圖 10 還顯示了 X 頻率和 Y 振幅參數。

圖 9. 生成正確的語法以複製並貼上到 LTspice 繪圖設定檔

圖 10. 添加傳導輻射通過/失敗線定義和頻率/振幅刻度

圖 11 顯示了傳導輻射限值線,以及降壓電路的 DM 和 CM 傳導輻射。電路在 2.3 MHz 至 30 MHz 頻段內未通過輻射測試。

圖 11. LTspice FFT 圖和 EN 55022 傳導輻射限值線

解決降壓轉換器 EMI

為了降低電路的 DM 雜訊,可以在輸入軌上放置一個 ESL 和 ESR 非常低的電容,例如 C12 22 µF Würth 885012209006,如圖 12 所示。

圖 12. 解決降壓轉換器輻射問題

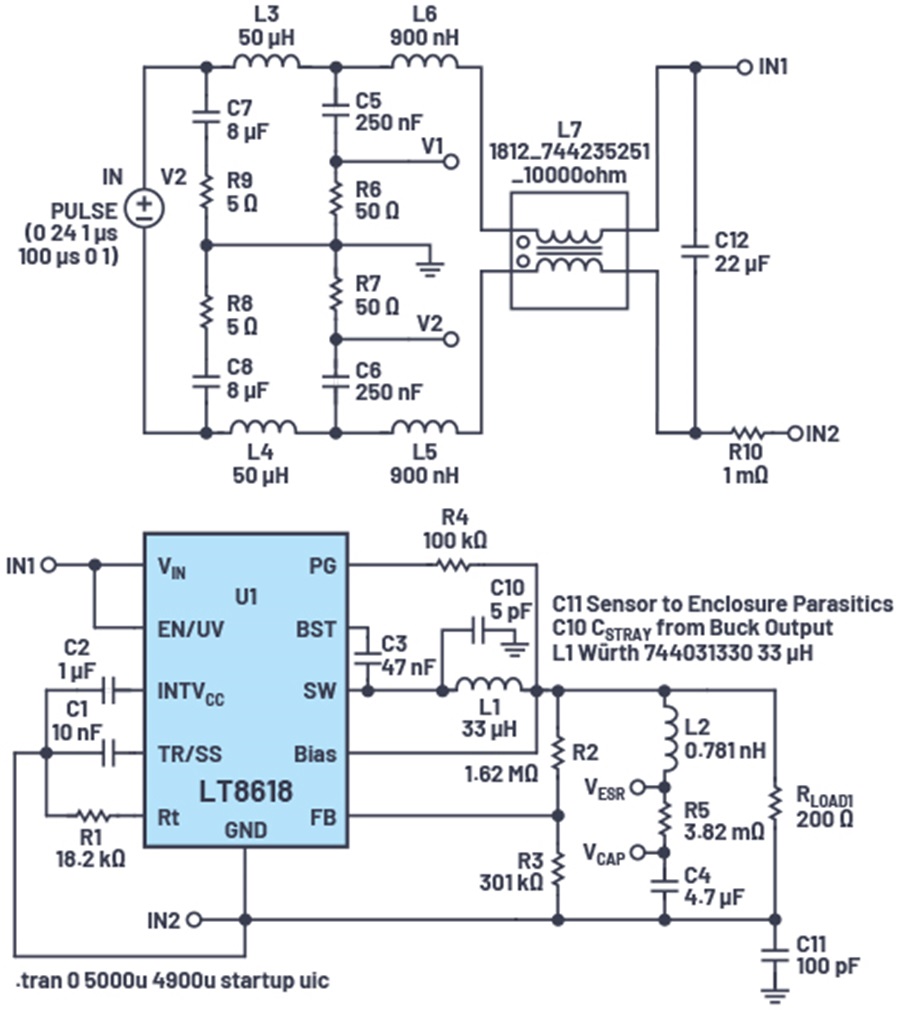

為了降低 CM 雜訊,可以從 LTspice 庫中選擇 Würth 共模扼流圈,例如 250 µH 744235251(WE-CNSW 系列)。封裝尺寸 4.5 mm × 3.2 mm × 2.8 mm 非常適合空間受限的 MEMS 感測器外殼。圖 13 顯示了問題解決後的降壓轉換器的 FFT 圖。

圖 13. 解決降壓轉換器問題後的 FFT 圖

使用 DC2822A LT8618 展示板的實際實驗室測量和模擬相關性

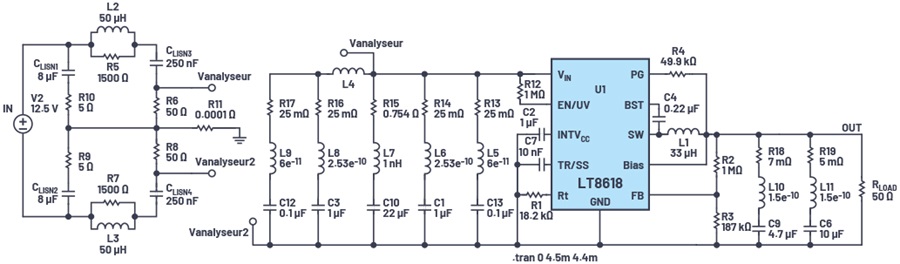

本文為 LTspice 進行傳導輻射模擬提供了指導。這些方法可用於任何降壓轉換器電路。現在我們將注意力轉向使用 DC2822A LT8618 展示板的模擬和 EMC 實驗室相關性,如圖 14 所示。DC2822A 展示板包括多個輸入和輸出電容,這些電容未包含在以前的模擬模型中(例如圖 7 和圖 12)。圖 15 中顯示的 LTspice 模型包括這些電容,以及使用 Würth REDEXPERT 獲得的電容 ESL 和 ESR 值。

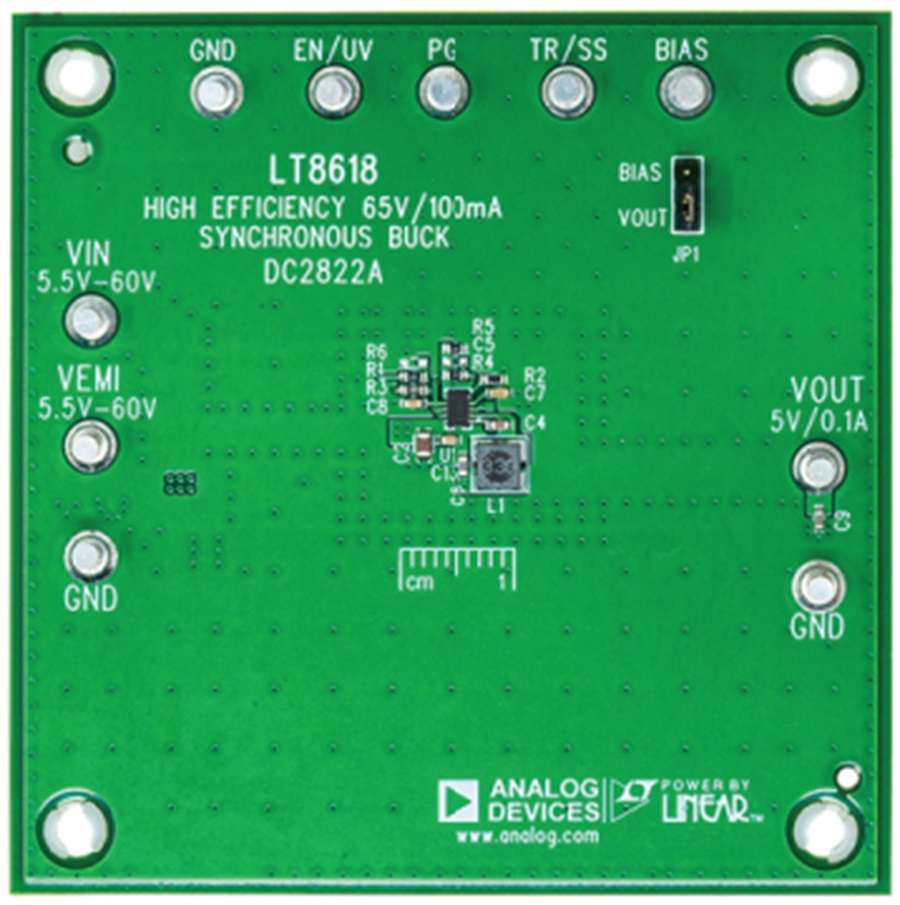

圖 14. DC2822A LT8618 展示板

圖 15. DC2822A 展示板 VIN 配置對應的 LTspice 模型

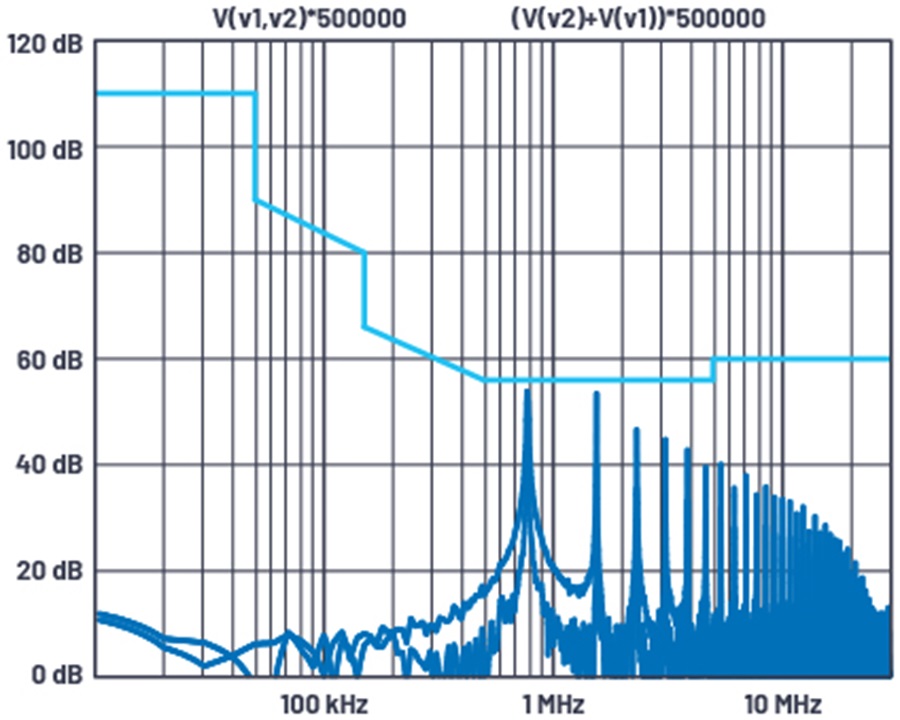

DC2822A 展示板包括兩個電源輸入:VIN 和 VEMI。VIN 輸入電源軌繞過了 PCB 上使用的鐵氧體磁珠。圖 15 LTspice 模型對應於展示板 VIN 配置。圖 16 顯示了 LTspice 模擬的 FFT,共模輻射在 2 MHz 時略微超過傳導輻射限值線。

圖 16. DC2822A VIN 配置對應的 LTspice FFT 圖

為了減少模擬時間,並最佳化 LTspice 模擬與 DC2822A 展示板實驗室測量的匹配度,相比之前的模型(圖 7 和圖 12),我們對圖 15 進行了以下更改:

-

無需模擬外殼和 PCB 之間的 100 pF 電容。我們只為 DC2822A 展示板建模。

-

從一開始就假設這個設計良好的 PCB 上的開關雜訊可以忽略不計。之前,我們在圖 7 和圖 12 中估計了 5 pF 的開關雜訊。

-

忽略 LISN 和 DC2822A 展示板之間導線的非常小電感。

-

添加 1 kΩ 電阻與 50 µH LISN 電感並聯以減少模擬時間(縮短 LISN 建立時間)。

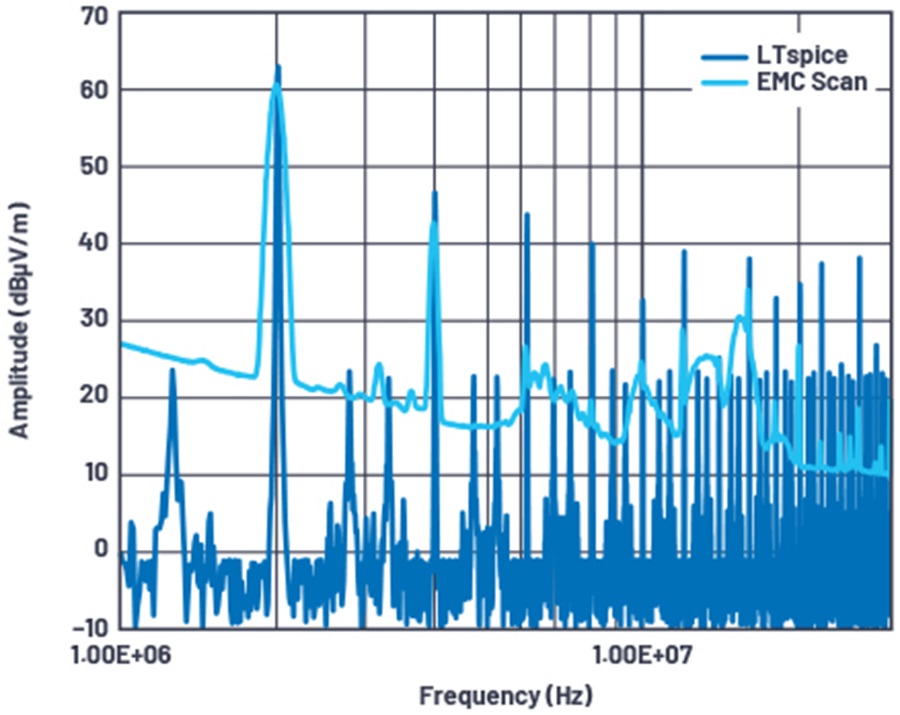

對圖 15 電路進行上述改變之後,圖 17 顯示了 LTspice 模擬與 EMC 實驗室中 DC2822A 展示板的實際測量的比較。LTspice 模擬模型非常準確地預測到實際實驗室輻射的主要峰值。

圖 17. DC2822A VIN 配置,LTspice 和實際 EMC 實驗室輻射的比較

透過鐵氧體磁珠(EMI 濾波器)VEMI 軌測量,DC2822A 展示板輕鬆符合 60 dBµV 的傳導輻射限值線。事實上,在較低頻率時,DC2822A 展示板只有 30 dBµV 至 35 dBµV 的輻射。

傳導抗擾度

有線狀態監控感測器具有嚴格的抗擾度要求。對於鐵路、自動化和重工業(例如紙漿和紙張加工)的狀態監控,振動感測器解決方案需要輸出低於 1 mV 的雜訊,以避免在數據採集/控制器處觸發錯誤的振動水準。這意味著電源設計向測量電路(MEMS 訊號鏈)輸出的雜訊必須非常低(低輸出漣波)。電源設計還必須不受耦合到電源電纜的雜訊的影響(高 PSRR)。

如前所示,由於非理想的電容性負載和叢發操作,LT8618 可能有數十毫伏的輸出漣波。對於 MEMS 感測器應用,LT8618 的輸出端需要一個超低雜訊和高 PSRR 的 LDO 穩壓器,例如 LT3042。

針對抗擾度 (PSRR) 的靈活模擬電路

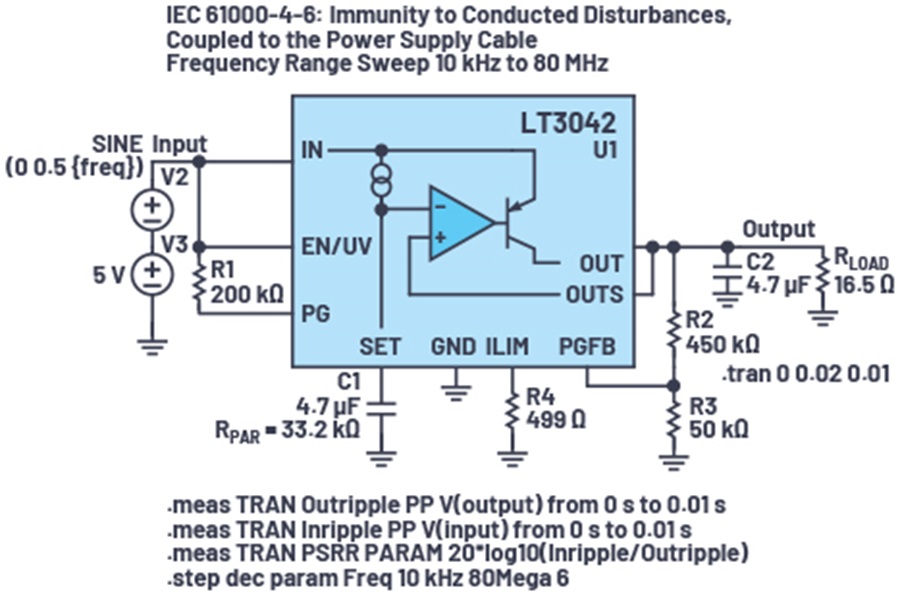

圖 18 所示的 LTspice 電路可用來模擬 LT3042 的 PSRR。圖 18 所示的時域瞬變模型是交流掃描方法的替代方法。這種時域模型比交流方法更靈活,甚至允許使用者對開關穩壓器的 PSRR 進行模擬。模擬電路頻率掃描電壓輸入軌的變化,並模擬輸出電壓的相應變化。換句話說,模擬評估如下方程式:$PSRR_{LT3042}$ = 頻率範圍內 (V_{IN} 變化)/(V_{OUT} 變化)。

圖 18. 在 10 kHz 至 80 MHz 範圍內模擬 LT3042 LDO 穩壓器的 PSRR

圖 18 含有幾個強大的語句。.meas 和 .step 語句的組合使用戶能夠在 LDO 輸入端添加電壓雜訊源,並在頻率範圍內測量電壓輸入階躍變化情況下的 LDO PSRR。

.meas 語句

允許使用者在一個時間範圍內測量訊號的峰對峰值並將其輸出到 SPICE 錯誤日誌。圖 18 測量了輸入和輸出漣波,並計算測量數據的 PSRR。所有這些都輸出到 SPICE 錯誤日誌中。

.step 語句

在單次模擬運行中,.step 命令可用於掃描變數的一系列值。圖 18 中的 .step 語句在 50 Hz 至 10 MHz 範圍內階躍改變 V2 電壓源正弦波。

C2 輸出電容初始電壓可設定為 3.3V,以加快建立(和模擬)時間。這是透過編輯電容屬性來完成的,透過禁用 LTspice 中的 "Start External DC Supply Voltage at 0 V" 選項可以進一步加快速度。

使用 SPICE 錯誤日誌

模擬完成後,右鍵點擊其中一個視窗,選擇檢視並選擇 SPICE 錯誤日誌(或使用 Ctrl+L 熱鍵)。SPICE 錯誤日誌包含 .meas 語句的數據點。

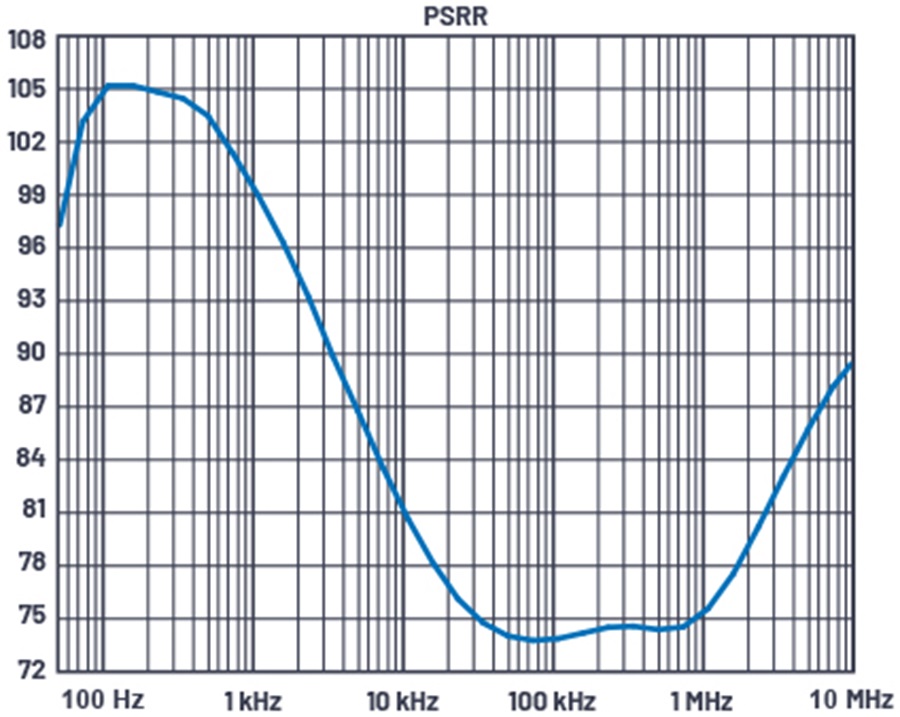

要繪製 .meas 數據圖,請右鍵點擊錯誤日誌並選擇繪製階躍 .meas 數據,右鍵點擊空白螢幕以選擇 "Add Trace"(添加軌跡,或使用 Ctrl+A)並選擇 PSRR。右鍵點擊 x 軸,選中單選按鈕以顯示對數刻度。這將顯示 PSRR 隨頻率的變化,如圖 19 所示。

圖 19. 繪製 LT3042 LDO 穩壓器的模擬 PSRR 圖

原始 LT3042 數據手冊曲線中的一些偽影不可見(約 2 MHz),但整體形狀和值與數據手冊接近。

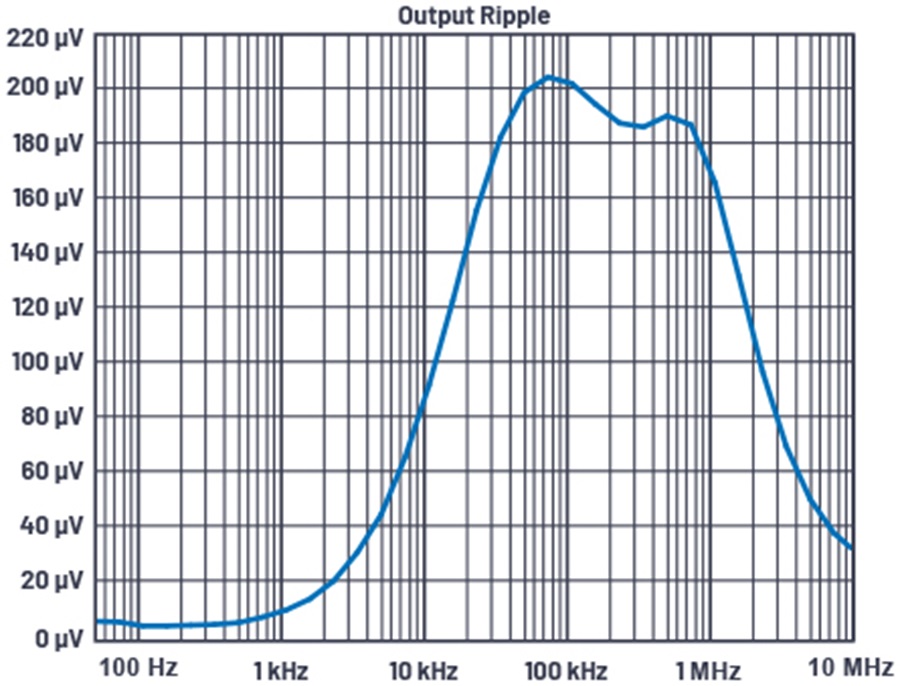

圖 20 顯示了頻率範圍內的輸出電壓漣波。在 50 Hz 至 10 MHz 範圍內,它小於 200 µV。在相同頻率範圍內,輸入電壓漣波為 1 V p-p。LT3042 為雜訊敏感的 MEMS 解決方案提供了出色的 PSRR 和低雜訊電源。

圖 20. 繪製 LT3042 模擬輸出電壓漣波隨頻率的變化圖

使用 SPICE 錯誤日誌的 .meas 方法可用來模擬許多其他參數,包括:

-

開關穩壓器的 PSRR

-

PSRR、電壓差與頻率三者的關係

-

PSRR 與旁路網路的關係

-

RMS 輸出漣波與直流輸入的關係

-

效率與元件值的關係

小結

本文提供了 LTspice 模擬電路和方法,用以繪製降壓轉換器電源設計的差模和共模雜訊圖。本文讓使用者能夠繪製傳導輻射限值線,並幫助預測 EMC 實驗室故障。模擬方法透過實驗室測量得到驗證,與 LT8618 DC2822A 展示板實測結果匹配。

在 LT8618 降壓轉換器的輸出端使用 LT3042 LDO 穩壓器,可為 MEMS 感測器應用提供超低雜訊、高 PSRR 解決方案。針對 PSRR 的靈活模擬電路表明結果與 LT3042 數據手冊有良好的一致性。在 50 Hz 至 10 MHz 範圍內,即使存在較大的 1 V p-p 輸入電壓雜訊,LT3042 的模擬輸出漣波也小於 200 µV。

關於作者

Richard Anslow

Richard Anslow 畢業於愛爾蘭利默里克大學,獲工程學士和碩士學位。他從事新產品定義工作,並且擔任面向客戶的角色,處理有關 ADI 隔離式通訊產品系列的問題。

Sylvain Le Bras

Sylvain Le Bras 是 Würth Elektronik 的一名現場應用工程師,專注於電源和電磁相容性。加入 Würth Elektronik 之前,Sylvain 在 ABB 和技術轉移實驗室擔任過多種研發職位。他畢業於法國南特大學理工學院,獲工程碩士學位。