使用 LTspice 確保 EMC 和訊號完整性

這是介紹 LTspice® EMC 和訊號完整性模擬模型的三篇系列文章的第二部分。在「如何使用 LTspice 獲得優異的 EMC 模擬結果 — 第一部分」中,我們介紹了針對電源元件、傳導輻射和抗擾度的 LTspice 模擬工具。

在第二部分中,我們將介紹 LTspice 和 C 語言程式的組合,旨在幫助設計人員了解和改善有線網路的訊號完整性。借助這些工具,設計人員無需多次進行實驗室測試迭代,也無需重新設計硬體。文中提供了符合以下標準的模擬模型:現場匯流排通訊(RS-485、RS-232)、高速背板 (LVDS)、無處不在的 USB 標準以及支持透過數據線供電 (PoDL) 的新型單對乙太網路 (SPE)。

為什麼設計人員應關心訊號完整性?

訊號完整性不僅指原型機擁有正常工作的鏈路。即使鏈路看起來有效,也建議您對訊號品質進行深入分析檢查,原因如下:

-

可靠性:距離、傳輸量和環境可能會導致二進位位元錯誤率 (BER) 提高,達到系統錯誤更正機制無法接受的程度。

-

IEEE 標準合規性:符合 IEEE 建議可確保網路成員之間無縫互連。

-

EMC 指令合規性:高轉動率 (High slew rate) 和過衝常常是不合規的原因,因為其含有高諧波成分。

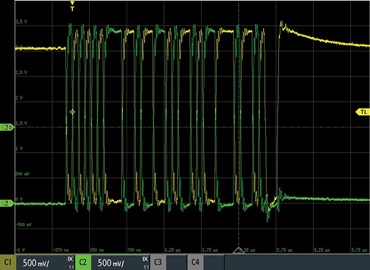

圖 1. 使用 LTspice 執行的分析範例

使用 LTspice 解決訊號完整性問題

本文將幫助設計人員回答若干關鍵問題,例如:

-

系統是否具有足夠的訊號完整性?

-

首先應該改善訊號的哪一方面?是否應該改善訊號轉動率、振鈴 (Ringing)、抖動 (Jitter) 或匹配?

-

系統正常工作,但隨著時間推移、溫度和元件容差的變化,它能否可靠地工作?

閱讀本文後,您應該能夠:

-

在 LTspice 中實施訊號完整性分析

-

產生、匯入和使用代表性測試向量,並產生類似圖 1 所示的分析和輸出

-

使用多個隨機參數對系統進行統計驗證

執行眼圖模擬

眼圖 (Eye Diagram) 提供了一種便捷的方法來評估傳送器或接收器端訊號是否一致。眼圖是基於時間的訊號表示。

這種表示方法使用餘輝 (Persistence) 方式來分析大量符號,並確保訊號位準、抖動和上升時間是適當的。

LTspice 具有眼圖分析所需的一些工具,但要執行全功能分析,需要實施一些額外的步驟。

使用測試向量產生 PWL 檔案

LTspice 提供了一種在模擬中使用測試向量的高效方法。為了更好地覆蓋可能導致不一致的情況,必須使用大量數據。

一些不一致情形會在非常特殊的情況下出現,例如:

-

長連續位元序列

-

非零平衡序列

-

來自附近其他傳輸通道的串擾

這意味著,假設數據是使用隨機函數產生的,為了確保遇到特定的 11 個連續高位準,可能必須使用數以千計的符號。

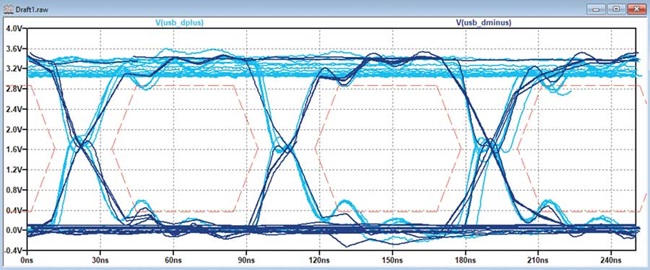

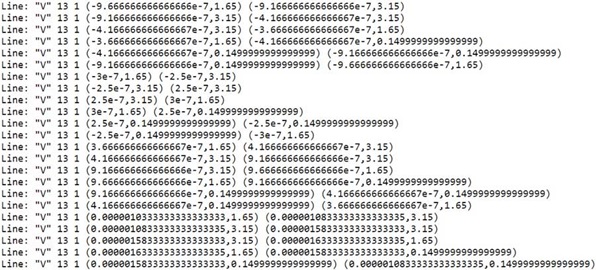

LTspice 期望的 PWL 數據格式如圖 2 所示。

圖 2. PWL 測試向量的檔案格式

其中:

-

第一個值是時間

-

第二個值是輸出(電壓、電流、溫度等)

-

->是定位字元 (Tab)(ASCII 碼 #09) -

CR 是歸位字元(ASCII 碼 #13)

-

LF 是換行字元(ASCII 碼 #10)

圖 3. 用於產生測試向量的程式碼摘錄

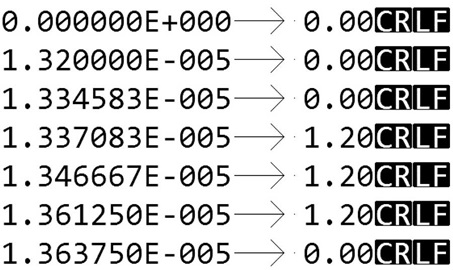

產生測試向量的方案有很多。這裡,我們選擇 C 語言。

只需幾行程式碼,就可以輕鬆產生大量可立即注入模擬的測試向量。圖 3 顯示了用於產生測試向量的程式碼摘錄,圖 4 顯示了 C 程式產生的波形。

圖 4. 使用 C 程式產生的測試向量

有線通訊中使用的概念(如位元填充/Bit stuffing)可以用幾行程式碼來實現,如圖 5 所示。

圖 5. 程式碼參見本文提供的連結。P1

使用擷取的測試向量產生 PWL 檔案

也可以使用實際數據並將數據匯入 LTspice。使用常規實驗室設備採集數據後,只需幾個步驟即可將其匯入。

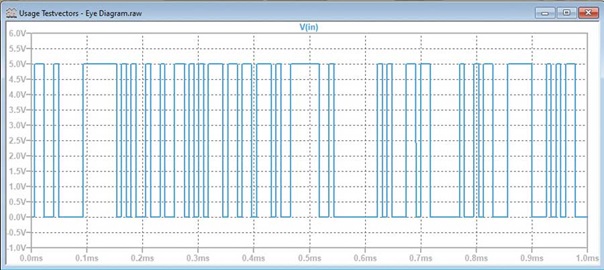

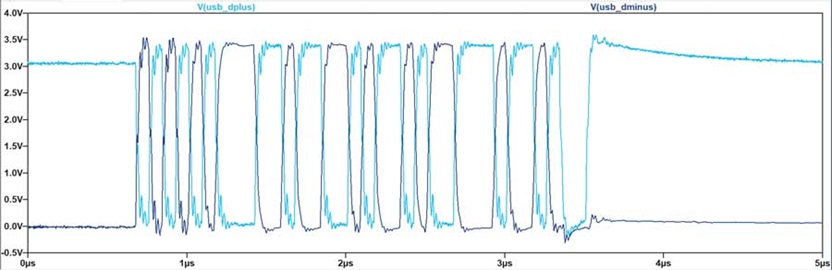

例如,圖 6 是使用示波器擷取的 USB 1.0 通訊訊號。

圖 6. 使用實驗室設備擷取的 USB 訊號

圖 7 是示波器儲存的資料集典型範例(具體格式可能有所不同,但將數據匯入 LTspice 的規則仍然適用)。

圖 7. 擷取的 USB 訊號的原始數據

要在 LTspice 模擬中使用此資料集,需要進行一些修改:

圖 8. LTspice 中匯入的 USB 訊號

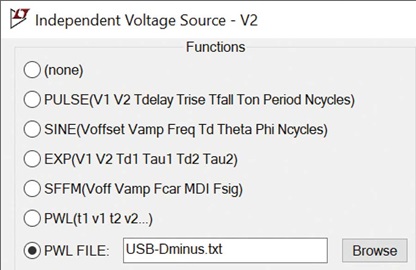

使用測試向量 PWL 檔案

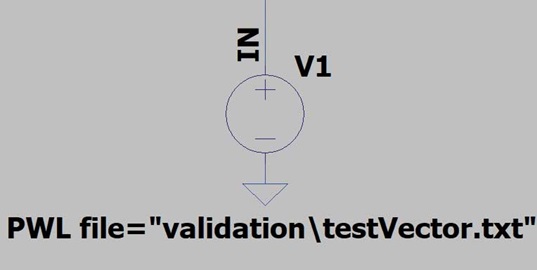

要使用產生的 PWL 檔案,可以向設計添加電壓源和檔案路徑,如圖 9 所示。

圖 9. 電壓源的 PWL 選項

絕對和相對檔案路徑均可使用,但建議使用相對路徑,使模擬可移植,以便與同事分享。

圖 10. 相對路徑範例

眼圖功能的啟用和調整

為了充分發揮 LTspice 這一隱藏功能的潛力,首先必須執行模擬。

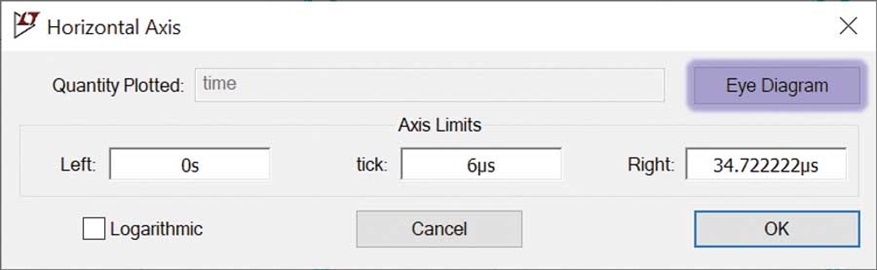

圖 11. 右鍵單擊該區域以啟用眼圖水平軸屬性

模擬完成並顯示訊號後,右鍵單擊水平(時間)軸。

隨即彈出一個對話框,顯示如圖 12 所示的眼圖按鈕。

圖 12. 眼圖選項的位置

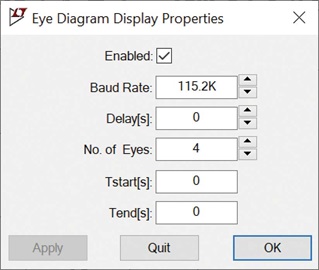

在此彈出視窗中,可以啟用和調整眼圖顯示,其中參數通俗易懂,無需解釋。

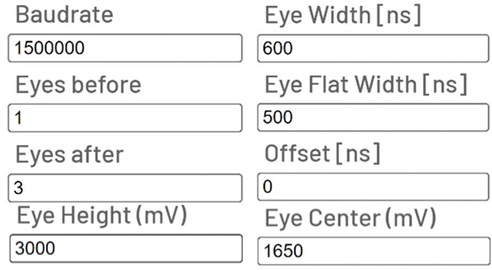

圖 13. 眼圖的設定

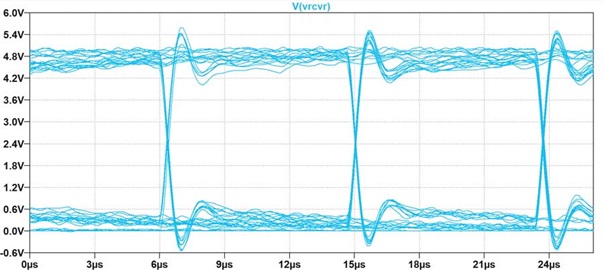

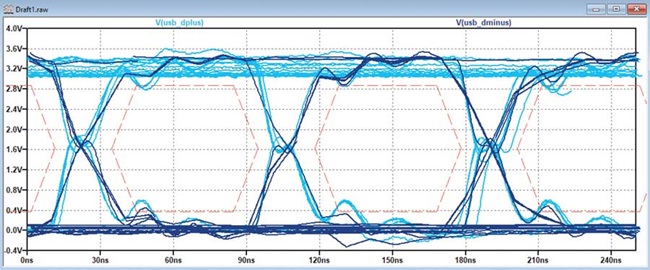

驗證後,顯示結果將如圖 14 所示。

圖 14. 眼圖顯示

計算和顯示眼圖模板

為了簡化對訊號完整性的評估,可以將眼圖與眼圖模板關聯。眼圖模板不是標準的 LTspice 功能,但仍然可以實現(類似第一篇文章中的 EMC 限值線)。

眼圖規格是一個標準,因此大部分遮罩可以透過一組精簡的變數進行評估,如圖 15 所示。

圖 15. 眼圖和眼圖模板

下面的列表給出了眼圖模板中字母 A 到 E 的定義:

-

A:眼圖平寬,在某些遮罩定義中它可以低至零。

-

B:眼寬,評估最大抖動、轉動率和鮑率等參數的關鍵。

-

C:眼高,根據您是在電纜的近端還是遠端評估此參數而有所不同。

-

D:眼圖中心,定義眼圖的中心電壓。

-

E:延遲,僅在 LTspice 中使用,以便在繪圖視窗內移動訊號。

產生眼圖模板

在本系列文章的第一部分中,我們說明了如何使用繪圖元件在 FFT 頻譜上顯示 EMC 限值線。在本文中,我們將展示如何使用相同的工具來繪製眼圖模板。

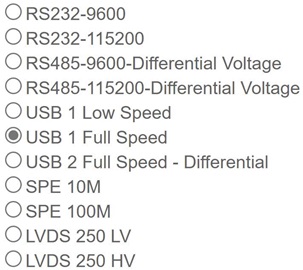

與產生和添加 EMC 限值線相比,眼圖的產生更為複雜。對於眼圖,我們使用含有 JavaScript P2 的網頁來產生眼圖定義,然後可以將其貼上到 LTspice 訊號顯示的繪圖設定檔 (*.plt) 中。如圖 16 所示,工程師可利用此 JavaScript 程式完成其設計。

常見有線介面標準的眼圖定義已作為預設提供。單擊每個無線電按鈕 (Radio button),欄位會自動填充典型值。

圖 16. 眼圖產生器的預設

使用提供的欄位也可以微調或實現您自己的眼圖定義。

圖 17. 眼圖模板輸入欄位

單擊更新按鈕就會產生相應的繪圖設定指令。您可以按照本系列文章第一部分所述的方法,將這些行添加到繪圖設定檔中。

圖 18. 由網頁產生的繪圖設定

為了獲得比較理想的顯示效果,可能需要調整要繪製的眼圖數量和 LTspice 延遲設定,如圖 19 所示。

圖 19. 由網頁產生的繪圖設定應用於波形

評估容差範圍內的一致性

設計中使用的元件具有較寬的容差,我們可以透過計算檢查這些容差是否會有問題。但是,當設計包含數百個元件時,使用紙筆或試算表等手動方法會非常耗時,並且可能無法捕獲重要參數。對於某些元件,可以使用更窄的容差,但如果為整個物料清單 (BOM) 挑選低容差元件的話,將會帶來價格和供貨問題,而且不會考慮老化或溫度相關性的影響。

為了在容差範圍內驗證設計,SPICE 及其擴充 LTspice 提供了幾個非常棒的工具。

以下部分介紹在 LTspice 中使用蒙地卡羅 (Monte Carlo) 和高斯分佈進行容差分析和最壞情況分析的方法。

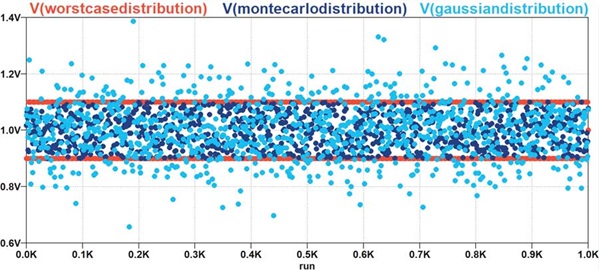

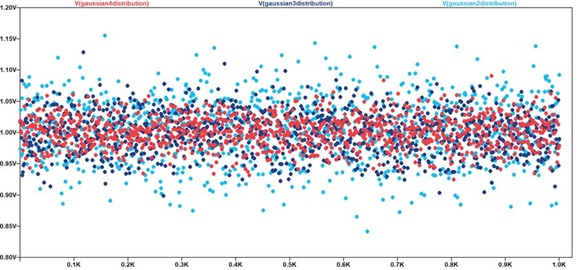

圖 20. 三種主要方法的隨機值分佈

高斯、最壞情況和蒙地卡羅方法的通用測試電路

為了比較這些方法在實際使用案例中的相關性和窮盡性,我們選擇了以下基於 Graber4 工作的範例。此設定顯示了 SPE 10Base-T1L 標準 (10SPE) 實體層或 MDI 的模擬電路。

圖 21 所示的模擬電路包括 $100\ \Omega \pm 10\%$ 的終端電阻,用於 ADI 公司的 ADIN1110 或 ADIN1100 10BASE-T1L 乙太網路 PHY/MAC-PHY。

訊號耦合電容、功率耦合電感、共模扼流圈和其他 EMC 保護元件均進行建模模擬。對於某些元件,我們添加了建議的元件值和容差範圍。

回波損耗圖的語法為:

(100+1/I(V1))/(100-1/I(V1))

蒙地卡羅模擬

蒙地卡羅模擬從模擬電路中每個指定元件的容差範圍中取一個隨機值。對於電路模擬而言,元件容差範圍內的所有值都有相等的機率。

LTspice 內建一個使用方便的蒙地卡羅功能,其語法很簡單。

例如,要建立一個容差為 10% 的 $100\ \Omega$ 電阻,就需要使用以下語法:

{mc(100R, ToIA)}

.param ToIA = 0.10

表 1. 使用蒙地卡羅方法定義元件值和容差標識範圍

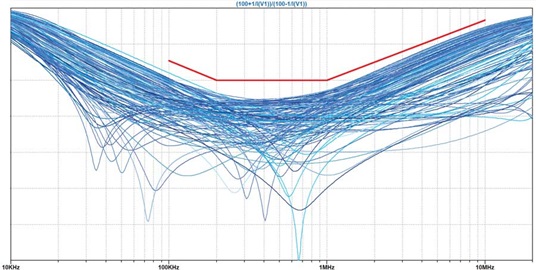

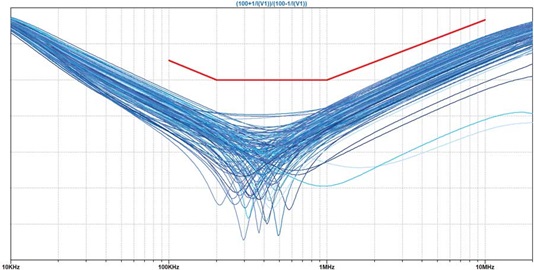

圖 21 所示的電路可用於模擬回波損耗 (Return Loss),它衡量所有可能發生的訊號反射。

回波損耗是由電纜鏈路上所有位置的阻抗不匹配引起的。回波損耗以分貝 (dB) 為單位,對於 10BASE-T1L 中採用的高數據速率或長電纜距離 (1700 m) 通訊尤為重要。

圖 21. 高斯、最壞情況和蒙地卡羅方法的通用測試電路 — 基於參考文獻 4

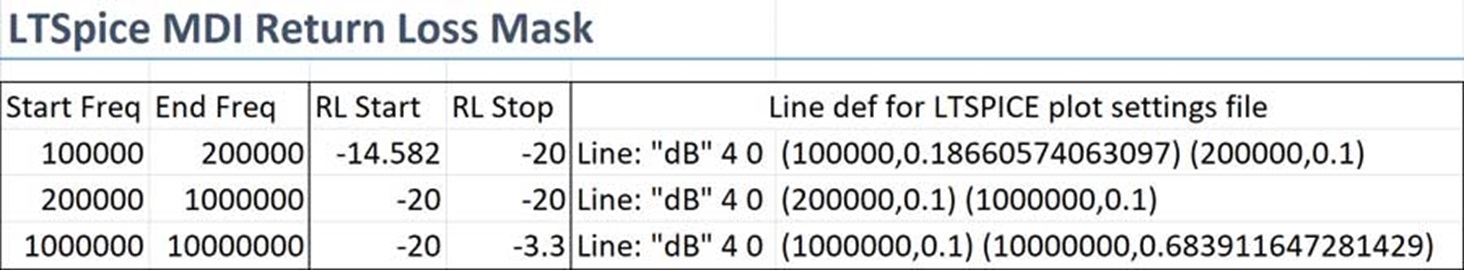

要將 MDI 回波損耗限值線添加到圖中(圖 23 中所示的紅線),請單擊 Plot Settings(繪圖設定)選單中的 Save Plot Settings(儲存繪圖設定)。

使用標準文字編輯器打開 .PLT 檔案。複製並貼上 Excel 檔案所示的線定義語法(圖 22)。

圖 22. LTspice 繪圖設定檔的線定義

要在模擬中得到理想的圖形,請右鍵單擊波形,然後單擊 Don't Plot Phase(不繪製相位)按鈕。

關於蒙地卡羅模擬的結論

蒙地卡羅模擬是評估電子設計在其容差範圍內的合規性的重要方法,很可能將滿足大多數設計人員的需求,同時模擬執行次數合理。

圖 23. SPE 終端的差動回波損耗:蒙地卡羅分佈參數的 128 次執行

最壞情況模擬

最壞情況模擬功能不是 LTspice 的內建功能。但是,您可以用所需函式來模擬最壞情況,如 Joseph Spencer 和 Gabino Alonso 的文章所述。

根據最壞情況執行模擬需要 .func binary(run,index) 和 .func wc(nom,tol,index) 函式,您需要將它們作為 SPICE 指令放在 LTspice 電路圖中。

.func binary(run,index) floor(run/(2**index))-2*floor(run/(2**(index+1)))

.func wc(nom,tol,index) if(run==numruns,nom,if(binary(run,index),nom*(1+ tol),nom*(1-tol)))

為了使用這些函式,您需要:

使用 numruns 宣告所需的模擬執行次數,這些執行次數應覆蓋每個進行最壞情況分析的元件的最大值、最小值和標稱值。執行次數為 $2^N+1$,其中 N 等於與元件容差相關的不同索引的數量。對於圖 21,執行次數為 129,因此語法為:

.param numruns = 129

您必須宣告以下表達式,而不是使用元件的常規值:

{wc(100R, 0.1, 0)}

其中:

-

100R 為標稱值

-

0.1 為容差(此處為 + 或 - 10%)

-

0 為要改變的參數的索引,下一個要改變的元件將採用索引 1

使用下表中的表達式(而不是靜態元件值)執行圖 21 所示的模擬電路:

表 2. 使用最壞情況方法定義元件值和容差標識範圍

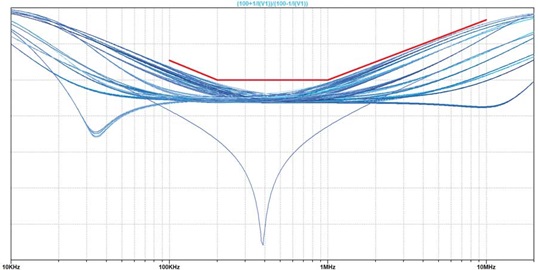

結果顯示在圖 24 所示的波形圖中。

透過編輯繪圖設定檔來添加 MDI 回波損耗遮罩限值線,如前文所述。

關於最壞情況分析的結論

Steve Knudtsen 簡要說明了系統設計使用最壞情況分析的優點和侷限性。

最壞情況分析是一種常見方法,其中會將元件參數調整到其最大容差極限。

最壞情況方法的侷限性包括:結果與通常觀察到的結果不一致;要觀察系統表現出最差性能,將需要裝配非常多的系統。

如果系統針對最壞情況進行設計,那麼選擇的元件可能會很昂貴。

然而,將最壞情況與蒙地卡羅或高斯模擬結合使用可以產生有價值的系統見解。

圖 24. SPE 終端的差動回波損耗:最壞情況分佈參數的 128 次執行

當模擬時間很長且標稱行為已經得到驗證時,最壞情況分析非常適合對系統行為進行總體驗證。

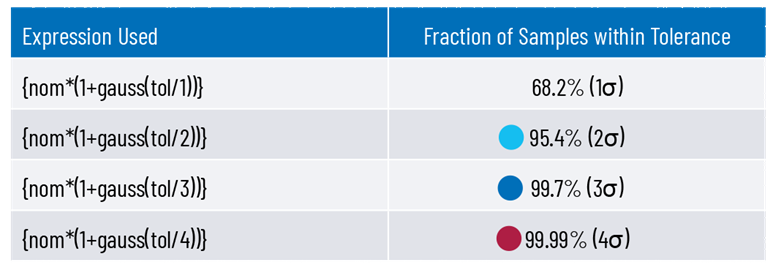

高斯模擬

LTspice 內建一個高斯函數,其中心值出現的機率較高。此高斯函數的語法很簡單。

{nominal_value*(1+gauss(tolerance/σ))}

要根據高斯分佈的標準差參數 $\sigma$ 進行調整,可以使用表 3 中的表達式。

表 3. 使用高斯分佈方法定義元件值和容差

或者使用更形象的表示:

圖 25. 樣本的高斯分佈與 $\sigma$ 的關係

例如,要建立一個容差為 10% 的 $100\ \Omega$ 電阻,並且值在容差內的機率為 $4\sigma$,您需要使用以下語法:

{100R*(1+gauss(ToIA/4))}

.param ToIA = 0.10

圖26提供了圖19所示模擬運行128次的結果,其中高斯模擬如圖19所示,高斯分佈參數使用4σ。

圖 26. SPE 終端的差動回波損耗:高斯分佈參數的 128 次執行

關於高斯分佈方法的結論

高斯分佈通常是模擬電子設計變化的重要方法。

參數圍繞標稱值的高斯分佈仍然是研究容差影響較自然的方法。

遺憾的是,這種方法代價不菲。為了詳盡無遺,模擬執行次數需要非常多。

此分佈還會選取容差範圍之外的值,省略元件製造商執行的排序和分級 (Binning) 操作。

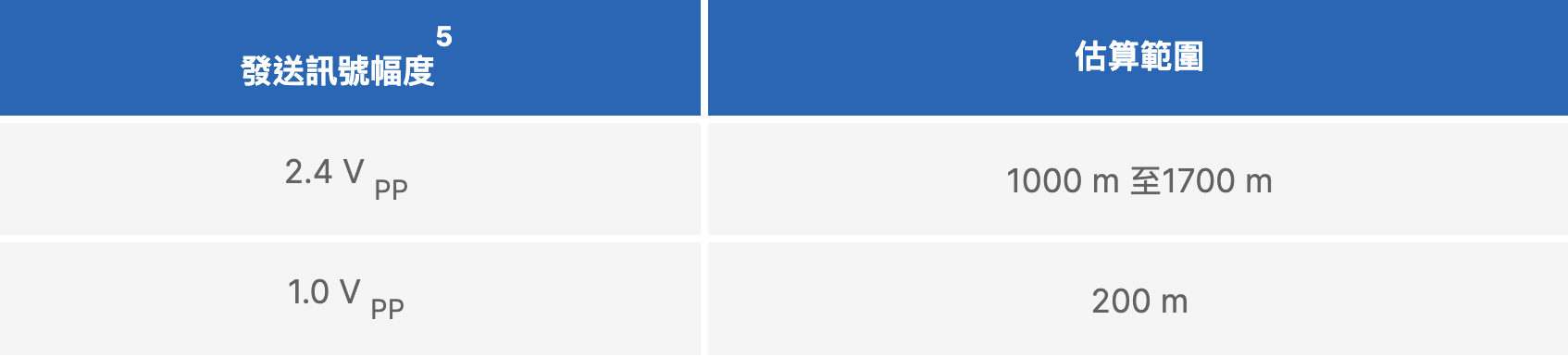

在 10BASE-T1L 鏈路分析中的應用

使用 10BASE-T1L 乙太網路標準的話,可以省去幾條現場匯流排。同一電纜既可用於傳統現場匯流排,也可用於 10BASE-T1L;它是一種簡單的平衡銅線對,用於全雙工通訊和為終端供電設備 (PD) 供電。雖然可以複用同一電纜,但必須更換實體層通訊收發器 (PHY) 和被動元件以滿足 10BASE-T1L 標準。

LTspice 中的大多數 10BASE-T1L 訊號完整性驗證可以使用類似形狀的訊號進行。

表 4. 單對乙太網路的範圍取決於傳送訊號振幅

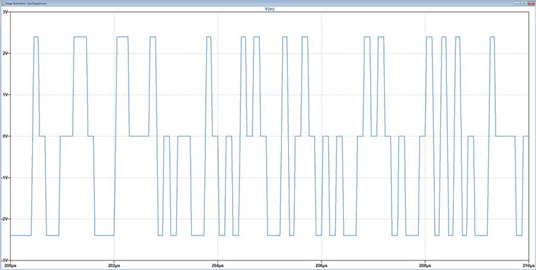

使用的編碼為 PAM3,用於脈衝振幅調變 3 級。根據端點期望的覆蓋範圍和能力,傳送訊號振幅可以調整為 1 V 或 2.4 V。

在電纜側,-1 至 +1 轉換的訊號上升時間為 53.33 ns,下降時間相同。

將轉動率 (Slew rate) 視為恆定,因此 0 至 1、1 至 0、-1 至 0 和 0 至 -1 轉換的標稱轉換時間應為 26.66 ns。

為了產生這樣的測試向量,我們將使用圖 27 中的程式碼。P3 它將以 PWL 格式輸出含有 5000 個 PAM3 符號的測試向量。

將此測試向量輸入到電路圖中,我們就能驗證各種參數,例如最小耦合、繞組間電容等等。

圖 28、29 和 30 分別顯示了 10BASE-T1L 鏈路基於變壓器的終端、PWL 源電壓檔案的輸出以及 PWL 電壓源和電纜側差動電壓的眼圖。這可用於 10BASE-T1L 標準合規性測試。

圖 27. 用於產生 PAM3 測試向量的程式碼摘錄

圖 28. 基於變壓器的終端,使用 PAM3 PWL 測試向量

圖 29. PWL 電壓源的輸出

圖 30. PWL 電壓源和電纜側差動電壓的眼圖

結論

LTspice 是一款功能強大且免費的模擬工具,可與使用標準 C 語言和 JavaScript 程式碼的波形產生器結合使用。最終,我們得到一種強大的有線通訊訊號完整性分析工具,其可用於節省實驗時間、指導最終產品設計並縮短產品開發時間,加速產品上市。ADI 和 Würth Elektronik 將為工程師提供該工具來設計有線鏈路,並幫助他們理解 10BASE-T1L SPE 等新標準。

關於作者

Richard Anslow

Richard Anslow 畢業於愛爾蘭利默里克大學,獲工程學士和碩士學位。他從事新產品定義工作,並且擔任面向客戶的角色,處理有關 ADI 隔離式通訊產品系列的問題。

Sylvain Le Bras

Sylvain Le Bras 是 Würth Elektronik 的一名現場應用工程師,專注於電源和電磁相容性。加入 Würth Elektronik 之前,Sylvain 在 ABB 和技術轉移實驗室擔任過多種研發職位。他畢業於法國南特大學理工學院,獲工程碩士學位。